財満・中塚研究室

最終更新日: 2018/1/15

研究テーマ

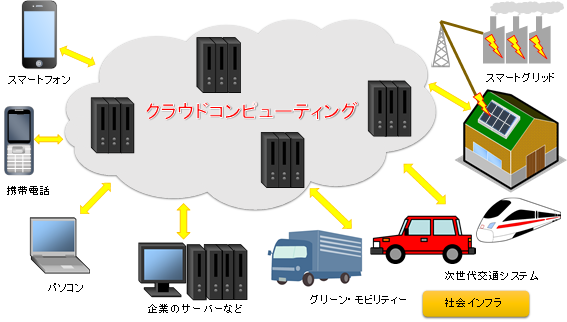

世界をもっと便利に、豊かにする 新しい半導体材料の探求現代の高度情報化社会において、スマートフォンなどの携帯端末機器やパソコンなどが常に「クラウドコンピューティング」を利用したデータセンターとアクセスし、どこでも便利で多様なサービスを受けられる時代となりました。また、クラウドコンピュー ティングによって、今後は電力の自由化に伴うスマートグリッドや、渋滞を緩和しスムーズな移動を可能にする次世代交通システムなどの高度なサービスの構築 が求められています。そのためには「通信の高速化」並びに携帯端末機器やパソコンなどの中核的な頭脳部分となる「半導体超々大規模集積回路(ULSI)」の「多機能化・高速化」が必須です。

一方、現在の日本におけるデータセンターの電力使用量は、全国で使用する電力の1%に達しています。今後、益々加速するクラウドサービスの利用を考える と、2018年には全世界で総消費電力の3%をサービスセンターが必要とすると予測されています。そのため、将来のULSIには高性能化だけでなく、「省電力化」技術も必要不可欠です。また、消費電力の低減と共に、地球規模での 環境負荷を減らすための「太陽光発電」などの再生利用エネルギーの積極的な利用と、その高効率化に向けた技術開発も必要となっています。

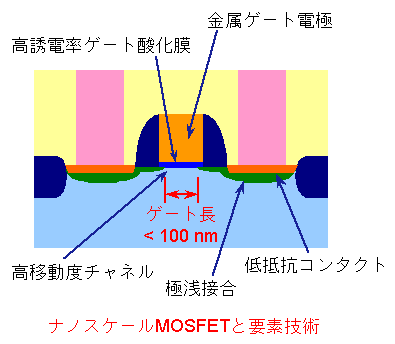

従来のシリコン(Si)ULSIの多機能化、高速化、省電力化は、これまで、回路を構成する基本素子である金属-酸化物-半導体電界効果型トランジスタ (MOSFET)の極微細化と高集積化によって達成されてきました。しかしながら、現在では、そのゲート長が14 nm(1nm=1000万分の1cm)の領域に突入した結果、理論的、技術的に様々な限界に直面しています。そのため、従来までの単純な極微細化と高集積化だけではさらなる性能向上は不可能となっています。将来のULSI性能向上のためには、Si にかわる新材料及び新構造の導入が必要不可欠です。近年、Fin-FETなどの3次元構造トランジスタ、新しい動作原理に基づくSteep Slope FET、3次元積層集積回路などの新材料、新構造、新技術の導入が検討されています。

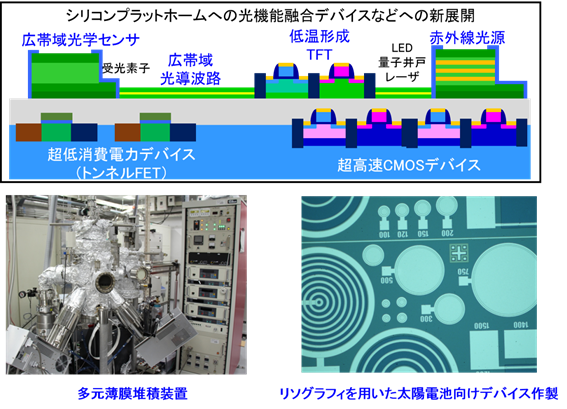

前述のような目標に向けて、我々の研究室では、シリコンに代表されるⅣ族系半導体材料をベースに、ナノメートルサイズの極微細トランジスタの高性能化や光電融合素子の実現のための、新しい材料の探索とデバイス構造設計、LSIの製造工程に関する研究開発などを進めています。

-

デバイス高速化・高性能化に向けたIV族多元混晶半導体ヘテロエピタキシャル成長技術

-

極微細MOSFETのための金属ゲート/高誘電率ゲート絶縁膜構造

-

極微細・超低抵抗・超平坦コンタクトのための金属/半導体界面反応制御

-

新世代デバイスに向けたナノ構造形成および観察技術

-

積層CMOSに向けた絶縁膜上の低温多結晶成長技術

-

自前発電デバイスの実現に向けたエネルギーハーベスティング技術

-

新世代デバイスに向けたナノ構造形成および観察技術

デバイス高速化・高性能化に向けたIV族系半導体ヘテロエピタキシャル成長技術

従来のSiと同じⅣ族半導体であるGeはSiより高移動かつ、Siとのプロセス親和性が高いため、次世代超高速デバイスに向けた半導体材料として期待されている。また、スズ(Sn)を導入したGe1-xSnxはSn組成によりバンドギャップ変調可能であり、8%以上のSn組成で直接遷移型半導体となり、更なる高移動度が期待できる材料です。また、Ge1-xSnxにSiを導入したSi1-x-yGeySnxでは三元混晶であるため、組成比によって格子定数とバンドギャプを独立に変調可能であり、Ge1-xSnxよりも材料の設計自由度が高くなります。これまで、我々の研究室ではSn組成8%を超えるGe1-xSnxや融点の異なる3つの原料を用いた難易度の高い三元混晶Si1-x-yGeySnxの結晶成長に関して分子線エピタキシー法を用いて低い成長温度で形成することによりGeなどの基板上にエピタキシャル成長させる事に成功しています。また、安全な有機金属材料(MO)を用いた化学気相成長(MOCVD)法を用いてGe1-xSnxを高品質に成長させる技術を確立してきました。

今後、MOSFETやトンネルFETなどの次世代デバイスに向けて、これらの材料の欠陥構造などを詳細に明らかにし、デバイスに必要な高品質化を行うと共にドーピング技術の確立を目指します。

極微細MOSFETのための金属ゲート/高誘電率ゲート絶縁膜構造

従来のSiやGeに対しては高温酸素雰囲気化で形成する熱酸化膜を利用することで非常に良好な界面を得られることが知られています。高誘電率ゲート絶縁膜とGeチャネルの間への、1 nm以下のGeO2の挿入が効果的であることがわかっています。しかしながら、Ge1-xSnxやSi1-x-yGeySnxなどのⅣ族多元混晶材料をチャネルに使ったデバイス作製に対して、高温熱酸化による酸化膜形成はSn析出のため困難です。これらⅣ族混晶材料のデバイス応用に向けて、より低温で良質な酸化膜および界面構造を形成することが必要です。本テーマでは高誘電率ゲート酸化膜とチャネル材料との間の極薄界面制御層形成に対し原子層堆法(ALD)を用いて低温で低界面準位密度となる成膜技術の確立を目指しています。極微細・超低抵抗・超平坦コンタクトのための金属/半導体界面反応制御

これまで、半導体ナノデバイスの省電力化に向けて、微細化やチャネル部分の半導体材料の移動度工場によりチャネル抵抗の低減に成功してきました。しかし、これに合わせて、寄生抵抗となるソース/ドレイン領域の金属との接触(コンタクト)抵抗のさらなる低減が必要となります。次世代半導体材料であるGeを用いたデバイス作製における問題点として、金属とGeとを接触させた時の障壁高さが仕事関数によらないフェルミレベルピニング現象が、従来材料のSiに比べてより顕著に表れることが知られています。これまで、ピニング現象の機構解明やその抑制を目的として、絶縁膜の挿入やエピタキシャルコンタクトなどの導入が検討されいますが、未だ抜本的解決には至っていません。我々は、Ⅳ族半導体混晶であるGeSnやSiGeSn界面層やエピタキシャル金属電極の活用に着目し、その電気伝導機構の解明と、これに基づく低抵抗コンタクトの形成を目指しています。積層CMOSに向けた絶縁膜上の低温多結晶成長技術

微細化に依存しないで高集積化を実現するため、縦方向への回路の積層が検討され始めています。その際、最も重要なのが、500℃以下の低温プロセスを用いることです。絶縁膜下層のデバイス特性に悪影響を与えないようにするためです。Siは800℃近い結晶化温度が必要ですが、Siに比べ融点の低いGe1-xSnxは500℃以下での結晶化が可能です。また、多結晶膜の移動度は粒界散乱等によりキャリア移動度が低くなってしまうため、Ge1-xSnxのようなSiよりも高いキャリア移動度を持つ材料の選択が重要です。単結晶Ge1-xSnxのキャリア移動度は電子・正孔ともにSiよりも高いため、多結晶でも比較的高い性能が得られると期待できます。我々は、Snの低い融点(231.9℃)を利用したGeの低温成長、水中レーザ結晶成長等に取り組み、最近、素子サイズに匹敵する大粒径Ge1-xSnx薄膜の低温・高品位形成の同時実現に成功しています。これらの成果は、世界初の多結晶GeSnFinFET及び省電力動作実証、および省電力動作には必須のCMOSインバータ動作(産総研との共同研究)に結実しています。