科学研究費補助金 特別推進研究

省電力/超高速ナノCMOSのための電子物性設計と高移動度チャネル技術の創生

(平成22年度−25年度)

【研究組織】

研究代表者 :

財満 鎭明 (名古屋大学・大学院工学研究科・教授)

研究分担者 :

田中 信夫 (名古屋大学・エコトピア科学研究所・教授)

竹中 充 (東京大学・大学院工学系研究科・准教授)

坂下 満男 (名古屋大学・大学院工学研究科・助教)

竹内 和歌奈 (名古屋大学・大学院工学研究科・助教)

田岡 紀之 (名古屋大学・大学院工学研究科・特任准教授)

連携研究者 :

中塚 理 (名古屋大学・大学院工学研究科・准教授)

高木 信一 (東京大学・大学院工学系研究科・教授)

【研究分野】

応用物理学・工学基礎、薄膜・表面界面物性

【キーワード】

薄膜、界面、半導体、エピタキシャル成長

【研究の背景・目的】

現代の高度情報化社会を支えるSi超々大規模集積回路(ULSI)は、その基本素子であるMOSトランジスタをスケーリング則に沿って微細化することで高速化と高集積化、高機能化を実現してきた。しかし、素子寸法がナノスケールに到達した現在では、材料の物性的限界から、これまでの微細化トレンドの維持が次第に難しくなり始めている。更に最近では、環境問題や携帯機器への応用の増大から、デバイスの一層の低消費電力化や高速化、高機能化などが求められている。

ULSIの超低消費電力化/超高速化においては、MOSトランジスタの電流駆動能力向上が不可欠である。現在でもSiの物性的限界を打破するために、Siに歪を加えてより高いキャリア移動度を得る技術が導入されている。しかし、この歪Siによる移動度向上にも限界が見えており、次世代ナノスケールULSIでは、歪Siを越える高移動度材料のチャネル領域への導入が不可欠となっている。

本研究では、ナノスケールCMOSの超低消費電力化と超高速化を実現するための高移動度チャネル技術の創成に向けて、歪Ge系チャネル材料の開発とその電子物性設計指針の構築を目指す。

【研究の方法】

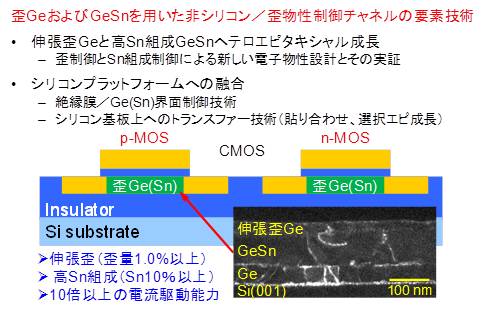

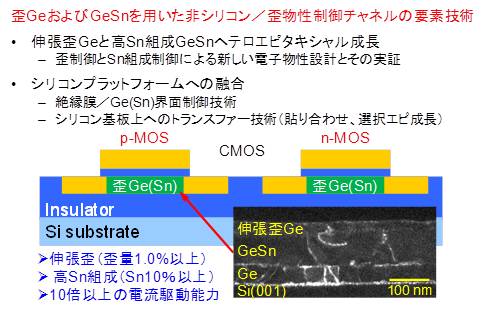

Geは電子、正孔共にSiを越える移動度を持つ材料として知られているが、歪SiのCMOS性能を越えるためには、電子移動度をさらに向上させる必要がある。Geに1%程度の伸張歪を印可すると電子と正孔共に歪Siの移動度を越えることが可能である。また、さらに大きな伸張歪の印加や20%程度のSnの添加により、バンド構造が直接遷移型に変化し、電子と正孔移動度が飛躍的に増加する可能性があることが予想されている。

これらのことを踏まえて本研究では、Si基板上に歪Geチャネルを実現することを目的として、歪Ge/GeSn/Siヘテロ構造作製のための基盤技術の確立と、歪Geおよび高Sn組成GeSnの電子物性の解明、MOS構造界面制御技術の提案などを行う。

【期待される成果と意義】

GeへのSn添加は、IV族系半導体材料に新しい物性や自由度をもたらすことができる。特に、次世代ナノCMOSのnチャネルとpチャネルMOSトランジスタの両方を、Siプロセスとの整合性の高いGe系材料で実現する可能性を拓くことができれば、現在考えられている次世代ULSI技術のトレンドを根本から変革することができるため、産業的なインパクトは極めて大きい。

さらに、この材料系は、高伸張歪印加や高組成Sn添加により直接遷移化が期待されるため、ULSI応用のみならず、太陽電池や受光・発光デバイスなどへの応用展開も大いに期待できる。